## GX85RS2MC

# Ferroelectric random access Memory (FRAM)

All rights reserved.

The Company and its subsidiaries and affiliates (hereinafter referred to as GXSC Storage) reserve the right to modify the contents of this manual without prior notice.

Please consult the sales representative of GXSC Storage before ordering the products. The information recorded in this manual, such as function summary and application circuit examples, is only provided to you as a reference for the use method and operation examples of GXSC Storage products; Wuxi Sunming Storage does not provide any express or implied warranties and shall not be liable for any damages for the information recorded in this manual, including but not limited to product quality, correctness,

functional performance, appropriateness of operation or infringement of products. If you import or install the products of Wuxi Shun Ming Storage into the products or devices developed by you based on the information recorded in this manual, you shall bear all risks and be responsible for all damages arising from this use. Wuxi Shun Ming Storage shall not be responsible for the information contained in this manual, or for any damage caused by your customer's use of this manual.

## Table of Contents

| 1. Description                       | 1  |

|--------------------------------------|----|

| 2. Features                          |    |

| 3. Pin Assignment                    | 2  |

| 4. Pin Functional Description        |    |

| 5. Block Diagram                     | 3  |

| 6. SPI Mode                          |    |

| 7. Serial Peripheral Interface       | 5  |

| 8. Status Register                   | 6  |

| 9. OP-Code                           | 8  |

| 10. Command                          | 8  |

| 11. Hold Operation                   |    |

| 12. Absolute Maximum Rating          | 15 |

| 13. Recommended Operation Conditions | 15 |

| 14. Electrical Characteristics       | 17 |

| 15. Timing Diagram                   | 19 |

| 16. Power On/Off Sequence            |    |

| 17.FRAM Characteristics              | 21 |

| 18. ESD and Latch-Up                 | 21 |

| 19. Package Dimension                | 22 |

## 1. Description

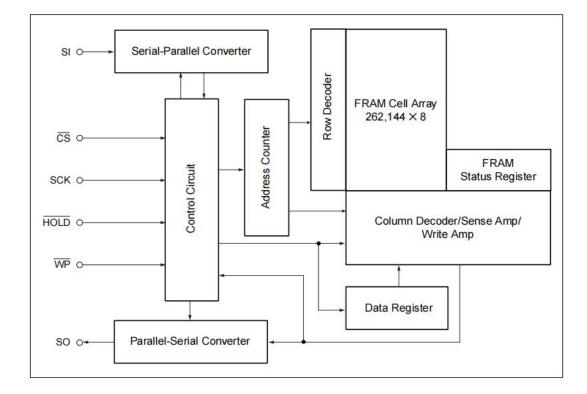

GX85RS2MC is a FRAM (Ferroelectric Random Access Memory) chip in a configuration of 262,144 w o r d s  $\times$  8 bits, using the ferroelectric process and silicon gate CMOS process technologies for forming the nonvolatile memory cells. Unlike SRAM, the chip does not require a battery to hold data.

The memory cells used in the GX85RS2MC can be used for 1E6 read/write operations<sup>\*1</sup>, which is more than FLASH and EEPROM. GX85RS2MC does not take long time to write data like Flash memories or E2PROM, and it takes no wait time.

| Capacity                               | 2M bit                                                             |

|----------------------------------------|--------------------------------------------------------------------|

| Interface                              | SPI interface (Mode 0 and mode 3)                                  |

| Operating voltage                      | 2.7V to 3.6V                                                       |

| Operating frequency                    | 25MHz                                                              |

| Power consumption                      | 4.8mA (25 MHz)                                                     |

| Low power<br>consumption               | 9uA (standby)                                                      |

| endurance                              | 106 Read/write (*1 room temperature), 109/ read (room temperature) |

| Data retention                         | 10 years @ 85C                                                     |

| Fast read<br>features                  | Support 40MHz fast read command                                    |

| Operation ambient<br>temperature range | -40°C to 85°C                                                      |

| Package                                | 8 pin SOP wide-body 208mil package, RoHS compliant                 |

### 2. Product Features

\*1: See Instructions for Use

Instructions for use:

O Total number of reading and writing defines the minimum value of endurance, as an FRAM memory operates with destructive readout mechanism.

recommend programming within the operation temperature range. Working beyond the temperature range for a long time cannot guarantee the data written within the normal temperature.

We recommend programming of the device after reflow. Data written before reflow cannot be guaranteed. Only once reflow soldering guaranteed.

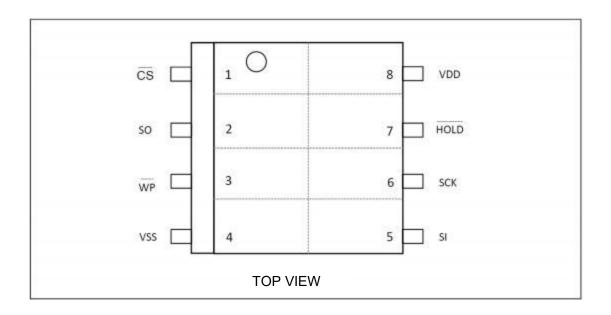

## 3. Pin Distribution

## 4. Pin function description

| Pin name | Function description                                                                                                                                                                                                                                                                                                                                                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| —<br>CS  | Chip Select pin<br>This is an input pin to make chips select. When CS is "H" level, device is in<br>deselect<br>(standby) status and SO becomes High-Z. Inputs from other pins are ignored for<br>this<br>time. When CS is "L" level, device is in select (active) status. CS has to be "L"<br>level before<br>inputting op-code. The Chip Select pin is pulled up internally to the VDD pin |

| SO       | Serial Data Output pin                                                                                                                                                                                                                                                                                                                                                                       |

| WP       | Write protect pin                                                                                                                                                                                                                                                                                                                                                                            |

| VSS      | Ground pin                                                                                                                                                                                                                                                                                                                                                                                   |

| SI       | Serial Data Input pin<br>This is an input pin of serial data. This inputs op-code, address, and<br>writing data                                                                                                                                                                                                                                                                              |

| SCK      | Serial Clock pin<br>This is a clock input pin to input/output serial data.                                                                                                                                                                                                                                                                                                                   |

| HOLD | Hold pin<br>This pin is used to interrupt serial input/output without making chips deselect.<br>When<br>HOLD is "L" level, hold operation is activated, SO becomes High-Z, SCK and SI<br>become |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD  | do not care. While the hold operation, CS has to be retained "L" level.<br>Power supply voltage pin                                                                                             |

## 5. Product block diagram

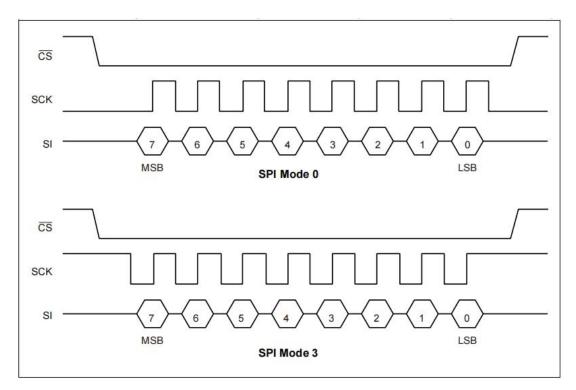

## 6. Interface mode

GX85RS2MC supports SPI mode 0(CPOL=0,CPHA=0) and SPI mode3(CPOL=1,CPHA=1) communication.

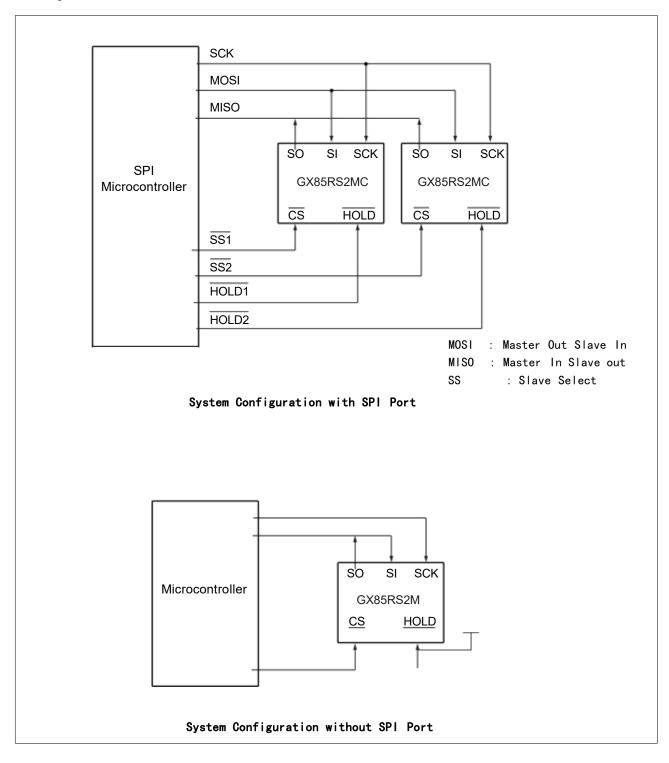

## 7. Serial peripheral interface

GX85RS2MC works as a slave of SPI. More than 2 devices can be connected by using microcontroller equipped with SPI port. By using a microcontroller not equipped with SPI port, SI and SO can be bus connected to use.

## 8. Status Register

| Bit number | Bit name | Function                                                                                                                                                                                                                                                                                  |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | WPEN     | Status Register Write Protect<br>This is a bit composed of nonvolatile memories (FRAM).<br>WPEN protects<br>writing to a status register (refer to "■ WRITING<br>PROTECT") relating with<br>WP input. Writing with the WRSR command and reading<br>with the RDSR<br>command are possible. |

| 6 to 4     | _        | Not Used Bits<br>These are bits composed of nonvolatile memories, writing<br>with the WRSR<br>command is possible. These bits are not used but they are<br>read with the<br>RDSR command.                                                                                                 |

| 3          | BP1      | Block Protect<br>This is a bit composed of nonvolatile memory. This defines                                                                                                                                                                                                               |

| 2          | BP0      | size of write<br>protect block for the WRITE command (refer to " <b>■</b> BLOCK<br>PROTECT").<br>Writing with the WRSR command and reading with the<br>RDSR command<br>are possible.                                                                                                      |

| 1 |   | Write Enable Latch<br>This indicates FRAM Array and status register are writable.<br>The WREN<br>command is for setting, and the WRDI command is for<br>resetting. With the<br>RDSR command, reading is possible but writing is not<br>possible with the<br>WRSR command. WEL is reset after the following<br>operations.<br>After power ON.<br>After WRDI command recognition.<br>The rising edge of CS after WRSR command recognition.<br>The rising edge of CS after WRITE command recognition. |

|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0 | This is a bit fixed to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## 9. OP code

GX85RS2MC accepts 9 kinds of command specified in op-code. Op-code is a code composed of 8 bits shown in the table below. Do not input invalid codes other than those codes. If CS is risen while inputting op-code, the command are not performed.

| Name  | Description              | Op-code    |

|-------|--------------------------|------------|

| WREN  | Set Write Enable Latch   | 0000 0110B |

| WRDI  | Reset Write Enable Latch | 0000 0100B |

| READ  | Read Memory Code         | 0000 0011B |

| WRITE | Write Memory Code        | 0000 0010B |

| RDID  | Read Device ID           | 1001 1111B |

| FSTRD | Fast Read Memory Code    | 0000 1011B |

| SLEEP | Sleep Mode               | 1011 1001B |

| RDSR  | Read status register     | 0000 0101B |

| WRSR  | Write status register    | 0000 0001B |

### 10. Command

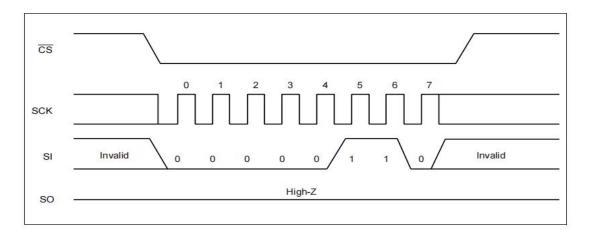

#### I WREN

The WREN command sets WEL (Write Enable Latch) . WEL has to be set with the WREN command before writing operation (WRSR command and WRITE command) . WREN command is applicable to "Up to 25 MHz operation"

#### WRDI

The WRDI command resets WEL (Write Enable Latch) . Writing operation (WRSR command and WRITE command) are not performed when WEL is reset. WRDI command is applicable to "Up to 25 MHz operation".

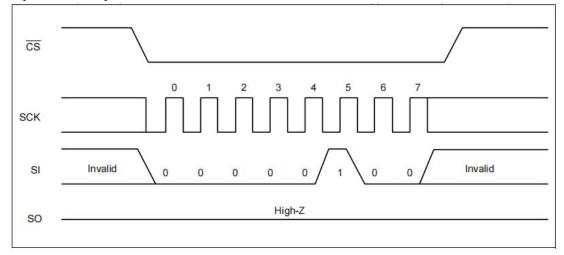

#### In RDSR

The RDSR command reads status register data. After op-code of RDSR is input to SI, 8-cycle clock is input to SCK. The SI value is invalid for this time. SO is output synchronously to a falling edge of SCK. In the RDSR command, repeated reading of status register is enabled by sending SCK continuously before rising of CS. RDSR command is applicable to "Up to 25 MHz operation".

#### I WRSR

The WRSR command writes data to the nonvolatile memory bit of status register. After performing WRSR op-code to a SI pin, 8 bits writing data is input. WEL (Write Enable Latch) is not able to be written with WRSR command. A SI value correspondent to bit 1 is ignored. Bit 0 of the status register is fixed to "0" and cannot be written. The SI value corresponding to bit 0 is ignored. WP signal level shall be fixed before performing WRSR command, and do not change the WP signal level until the end of command sequence. WRSR command is applicable to "Up to 25 MHz operation".

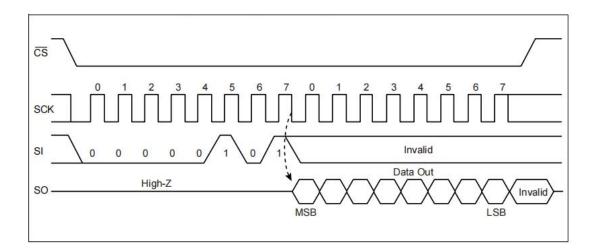

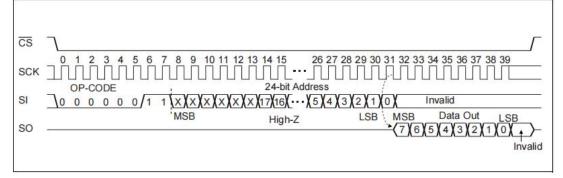

#### READ

The READ command reads FRAM memory cell array data. Arbitrary 24 bits address and op-code of READ are input to SI. The 6-bit upper address bit is invalid. Then, 8-cycle clock is input to SCK. SO is output synchronously to the falling edge of SCK. While reading, the SI value is invalid. When CS is risen, the READ command is completed, but keeps on reading with automatic address increment which is enabled by continuously sending clocks to SCK in unit of 8 cycles before CS rising. When it reaches the most significant address, it rolls over to the starting address, and reading cycle keeps on infinitely. READ command is applicable to "Up to 25 MHz operation".

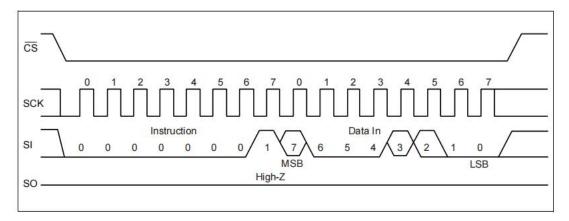

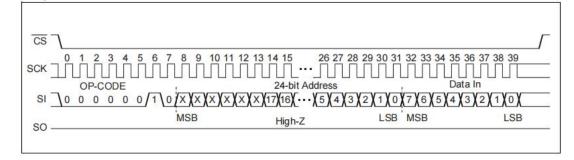

#### WRITE

The WRITE command writes data to FRAM memory cell array. WRITE op-code, arbitrary 24 bits of address and 8 bits of writing data are input to SI. The 6-bit upper address bit is invalid. When 8 bits of writing data is input, data is written to FRAM memory cell array. Risen CS will terminate the WRITE command, but if you continue sending the writing data for 8 bits each before CS rising, it is possible to continue writing with automatic address increment. When it reaches the most significant address, it rolls over to the starting address, and writing cycle can be continued infinitely. WRITE command is applicable to "Up to 25 MHz operation".

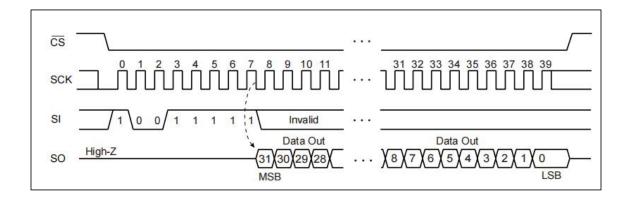

#### I FSTRD

The FSTRD command reads FRAM memory cell array data. Arbitrary 24 bits address and opcode of FSTRD are input to SI followed by 8 bits dummy. The 6-bit upper address bit is invalid. Then, 8-cycle clock is input to SCK. SO is output synchronously to the falling edge of SCK. While reading, the SI value is invalid. When CS is risen, the FSTRD command is completed, but keeps on reading with automatic address incrementwhich is enabled by continuously sending clocks to SCK in unit of 8 cycles before CS rising. When it reaches the most significant address, it rolls over to the starting address, and reading cycle keeps on infinitely. FSTRD command is applicable to 40 MHz (2.7 V to 3.6 V) operation.

| CS  |                                                                                                           |   |

|-----|-----------------------------------------------------------------------------------------------------------|---|

| SCK | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 1415 29 30 31 32 33 38 39 40 41 42 43 44 45 46 47                         | - |

| SI  | OP-CODE 24-bit Address 8-bit Dummy<br>0 0 0 0 1 0 1 1 X X X X X X X X 17/16 X 2 1 1 0 X X X X X X Invalid | - |

| 0   | MSB High-Z LSB MSB Data Out LSB                                                                           | - |

| SO  |                                                                                                           | - |

|     | Invali                                                                                                    | a |

#### RDD

The RDID command reads fixed Device ID. After performing RDID op-code to SI, 32-cycle clock is input to SCK. The SI value is invalid for this time. SO is output synchronously to a falling edge of SCK. The output is in order of Manufacturer ID (8bit)/Continuation code (8bit)/Product ID (1st Byte)/Product ID (2nd Byte). In the RDID command, SO holds the output state of the last bit in 32-bit Device ID until CS is risen. RDID command is applicable to "Up to 25 MHz operation". Chip ID : Hexadecimal 628C 2400

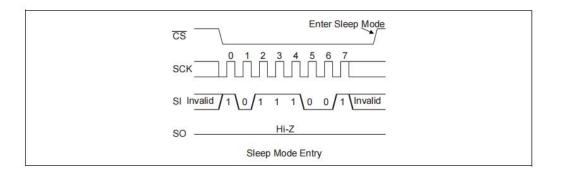

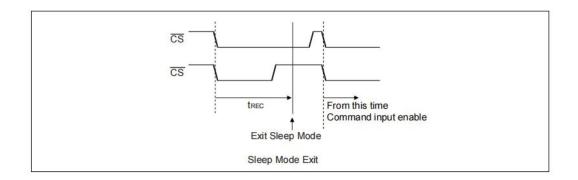

#### I SLEEP

The SLEEP command shifts the LSI to a low power mode called "SLEEP mode". The transition to the SLEEP mode is carried out at the rising edge of CS after operation code in the SLEEP command. However, when at least one SCK clock is inputted before the rising edge of CS after operation code in the SLEEP command, this SLEEP command is canceled.

After the SLEEP mode transition, SCK and SI inputs are ignored and SO changes to a Hi-Z state

Returning to an normal operation from the SLEEP mode is carried out after tREC (1us) time from the falling edge of CS (see the figure below). It is possible to return CS to H level before tREC time. However, it is prohibited to bring down CS to L level again during tREC period

#### Block Protection

The WRITE protection block of the write command is configured by the values of BP0 and BP1 in the status register.

| BP1 | BPO | Protected Block                                             |  |  |

|-----|-----|-------------------------------------------------------------|--|--|

| 0   | 0   | None                                                        |  |  |

| 0   | 1   | $30000_{\text{H}}$ to $3\text{FFFF}_{\text{H}}$ (upper 1/4) |  |  |

| 1   | 0   | 20000н to 3FFFFн (upper 1/2)                                |  |  |

| 1   | 1   | 00000н to 3FFFFн (all)                                      |  |  |

#### Write Protection

Writing operation of the WRITE command and the WRSR command are protected with the value of WEL, WPEN, WP as shown in the table.

| WEL | WPEN | WP | Protected Blocks | Unprotected Blocks | Status Register |  |

|-----|------|----|------------------|--------------------|-----------------|--|

| 0   | Х    | Х  | Protected        | Protected          | Protected       |  |

| 1   | 0    | Х  | Protected        | Unprotected        | Unprotected     |  |

| 1   | 1    | 0  | Protected        | Unprotected        | Protected       |  |

| 1   | 1    | 1  | Protected        | Unprotected        | Unprotected     |  |

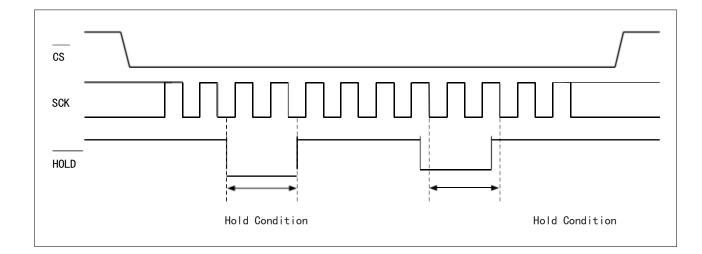

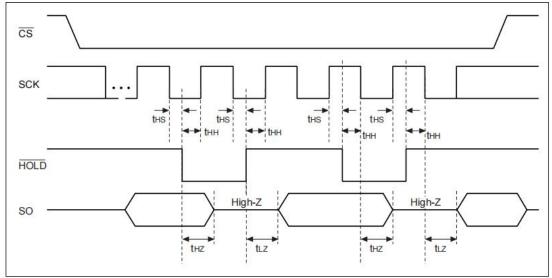

## **11 Hold operation**

Hold status is retained without aborting a command if HOLD is "L" level while CS is "L" level. The timing for starting and ending hold status depends on the SCK to be "H" level or "L" level when a HOLD pin input is transited to the hold condition as shown in the diagram below. In case the HOLD pin transited to "L" level when SCK is "L" level, return the HOLD pin to "H" level at SCK being "L" level. In the same manner, in case the HOLD pin transited to "L" level when SCK is "H" level, return the HOLD pin to "H" level at SCK being "L" level, return the HOLD pin to "H" level at SCK being "H" level. Arbitrary command operation is interrupted in hold status, SCK and SI inputs become do not care. And, SO becomes High-Z while reading command (RDSR, READ). If CS is rising during hold status, a command is aborted. In case the command is aborted before its recognition, WEL holds the value before transition to hold status.

| Parameters                       | Symbols | Rating  | Rating    |    |

|----------------------------------|---------|---------|-----------|----|

|                                  |         | Minimum | Maximum   |    |

| Supply voltage                   | VDD     | -0.5    | 4.0       | V  |

| Input voltage                    | V IN    | -0.5    | VDD + 0.5 | V  |

| Output voltage                   | VOUT    | -0.5    | VDD + 0.5 | V  |

| Operation ambient<br>temperature | ТА      | -40     | 85        | °C |

| Storage temperature              | Tstg    | -40     | 125       | °C |

## 12. Absolute maximum rating

\*1: The above parameter values are based on VSS = 0V.

\*2: The above storage temperature is the ambient temperature that the device can store before writing data. After the device writes data, please refer to the working ambient temperature

< Warning > Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or temperature) in excess of absolute maximum ratings.

Do not exceed any of these ratings.

### **13. Recommended working conditions**

|                                     |     | Numerical val |     |                  |       |

|-------------------------------------|-----|---------------|-----|------------------|-------|

| Parameters                          |     |               | 21  | Maximum<br>value | Units |

| Supply voltage                      | VDD | 2.7           | 3.3 | 3.6              | V     |

| Operation<br>ambient<br>temperature | ТА  | - 40          |     | + 85             | °C    |

\*1: The above parameter values are based on VSS = 0V

\*2: Only applicable to the ambient temperature of the chip during operation. It can be understood that this temperature is almost the same as the temperature of the chip surface.

< Warning > In order to ensure the normal operation of the semiconductor device, it must be used in the recommended operating environment or conditions.

All electrical characteristics of the device can be guaranteed when operating in the recommended environment or condition. Be sure to use the semiconductor device within the recommended operating environment or condition. If used outside this range, it may affect the reliability of the device and cause failure.

The Company does not guarantee any scope of use, operating conditions or logical combinations not recorded in this data sheet. If the user wishes to use the device outside the conditions listed, it is important to contact the sales representative in advance.

## 14. Electrical characteristics

Dc characteristics

(within recommended operating conditions)

|                                    |                |                                                                                                                       | Numerical value       |      |                       |       |  |

|------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|--|

| Parameters                         | Symb<br>ols    | Conditions                                                                                                            | Minimum               |      | Maximum<br>value      | Units |  |

| Input leakage<br>current           | ا ار ا         | $V_{\text{IN}} = 0 \text{ V to } V_{\text{DD}}$                                                                       | _                     | _    | 1                     | μA    |  |

| Output<br>leakage<br>current       | <sub>ko</sub>  | $V_{\text{OUT}} = 0 V \text{ to } V_{\text{DD}}$                                                                      | _                     | _    | 1                     | μA    |  |

| Working<br>power supply<br>current | lod            | SCK = 25MHz<br>SO = open                                                                                              | -                     | 4. 8 | 5.6                   | mA    |  |

| Standby<br>current                 | lsв            | $SCK = SI = \overline{CS} = V_{DD}$                                                                                   | _                     | 9    | 12                    | μA    |  |

| Sleep current                      | lzz            | $\overline{\text{CS}} = \text{V}_{\text{DD}}$<br>All other inputs $\text{V}_{\text{SS}}$ or<br>$\text{V}_{\text{DD}}$ | _                     | 3    | 4                     | μA    |  |

| Input high<br>voltage              | V IH           | $V_{DD} = 2.7V$ to 3.6V                                                                                               | V <sub>DD</sub> * 0.7 | _    | V <sub>DD</sub> + 0.3 | v     |  |

| Input low<br>voltage               | V IL           | $V_{DD} = 2.7V$ to 3.6V                                                                                               | 0. 5                  | _    | V <sub>DD</sub> * 0.3 | v     |  |

| Output high<br>voltage             | Vон            | $I_{oH} = -2mA$                                                                                                       | $V_{DD} - 0.5$        | _    | V <sub>DD</sub>       | v     |  |

| Output low<br>voltage              | Vol            | $I_{oL} = 2mA$                                                                                                        | Vss                   | _    | 0.4                   | v     |  |

| CS Pull up<br>resistors            | R <sub>P</sub> | _                                                                                                                     | 18                    | 33   | 80                    | kΩ    |  |

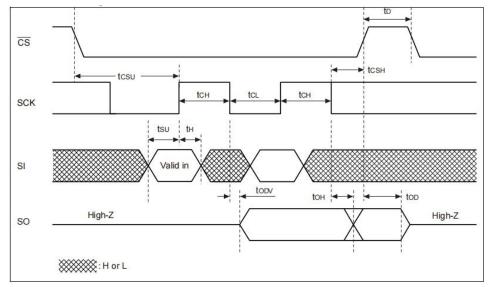

#### Numerical sym Parameter unit bol Min Max Clock frequency (commands 0 25 f<sub>ск</sub> MHz other than FSTRD) Clock frequency (FSTRD 0 40 f<sub>ск</sub> MHz command) Clock high level time ${\tt t}_{\tt CH}$ 11 \_\_\_\_ ns Clock low time 11 ns ${\tt t}_{\tt CL}$ 10 \_\_\_\_ Chip select setup time $t_{\text{csu}}$ ns Chip select hold time 10 ns $t_{CSH}$ 12 Output disabled time $t_{\text{OD}}$ \_\_\_\_ ns Output data valid time \_\_\_\_ 9 $t_{\text{ODV}}$ ns Output hold time 0 \_\_\_\_ $t_{\text{OH}}$ ns 40 Deselect time $t_{\scriptscriptstyle D}$ ns Data on rise time \_\_\_\_ 50 ns $t_{\scriptscriptstyle R}$ Data drop time \_\_\_\_ 50 t ns 5 Data setup time ns $t_{su}$ Data retention time 5 t<sub>H</sub> ns 10 $t_{\scriptscriptstyle HS}$ ns HOLD Set time 10 ns $t_{\text{HH}}$ HOLD Hold time 20 \_\_\_\_ ns $t_{\rm HZ}$ HOLD Output float time 20 HOLD Output activation $t_{\text{LZ}}$ ns time SLEEP exit time 1 \_\_\_\_ $t_{\text{REC}}$ μs

#### Communication characteristics

#### **Communication Test conditions**

Pin capacitance

| Parameters            | Symbol s Conditions |                                                                         | Numerical value |         | Units |

|-----------------------|---------------------|-------------------------------------------------------------------------|-----------------|---------|-------|

|                       |                     |                                                                         | Minimum         | Maximum |       |

| Output<br>capacitance | Co                  | $V_{DD} = V_{IN} = V_{OUT} = 0V,$<br>f = 1 MHz, T <sub>A</sub> = +25 °C | -               | 10      | pF    |

| Input<br>capacitor    | C ,                 | Γ - Tmiz, Τ <sub>Α</sub> - ΤΖΟ C                                        | _               | 10      | pF    |

## 15. Timing chart

Serial Data Timing

Hold timing

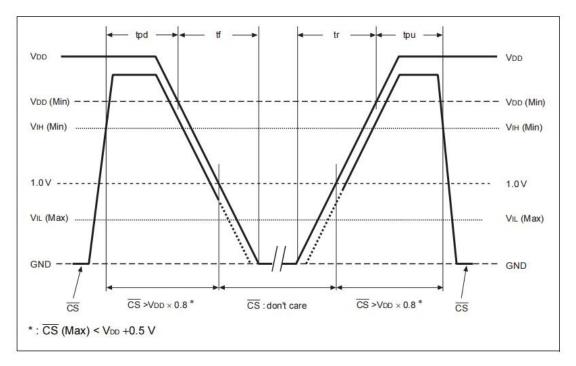

## 16. Power on/off timing

| Parameters                      | Symbols        | Numerical value |         | Units |

|---------------------------------|----------------|-----------------|---------|-------|

|                                 |                | Minimum         | Maximum |       |

| CS level hold time at power OFF |                |                 |         |       |

|                                 | $t_{pd}$       | 200             | -       | ns    |

|                                 |                |                 |         |       |

| CS level hold time at power ON  |                |                 |         |       |

|                                 | $t_{pu}$       | 50              | -       | μs    |

|                                 |                |                 |         |       |

| Power supply falling time       | t <sub>f</sub> | 20              | -       | μs    |

| Power supply rising time        | t,             | 20              | _       | μs    |

Note: Storage of data is not guaranteed if the device cannot operate within specific conditions of read cycle, write cycle, or power on/off timing.

## **17.FRAM** features

| Parameters                      | Minimum | Maxim | Units      | Remarks                                            |

|---------------------------------|---------|-------|------------|----------------------------------------------------|

|                                 | value   | um    |            |                                                    |

|                                 | 1E6     |       | Times/byte | operation ambient temperature $T_A = -40$ °C       |

| Read and<br>write               | 1E6     |       | Times/byte | operation ambient temperature $T_A = +25^{\circ}C$ |

| endurance*1                     | 1E5     |       | Times/byte | operation ambient temperature $T_A = +85^{\circ}C$ |

|                                 | _       |       | year       | operation ambient temperature $T_A = -40^{\circ}C$ |

| Data<br>retention <sup>*2</sup> |         |       | year       | operation ambient temperature $T_A = +25^{\circ}C$ |

|                                 | 10      |       | year       | operation ambient temperature $T_A = +85^{\circ}C$ |

\*1: Total number of reading and writing defines the minimum value of endurance, as an FRAM memory

operates with destructive readout mechanism; See "Instructions for Use" for details.

\*2: Data retention years indicate the data retention time after the first read and write operation after delivery from the factory. These retention times are converted values based on reliability assessment results; See the Instructions for Use for details

## 18 ESD and latch

| Test                                                | Numerical value |  |

|-----------------------------------------------------|-----------------|--|

| ESD HBM (mannequin)<br>JS-001 compliant             | ≥  2000 V       |  |

| ESD CDM (Charging device model)<br>JS-002 compliant | ≥  1000 V       |  |

| Latch-up<br>Comply with JESD78                      | ≥  300 mA       |  |

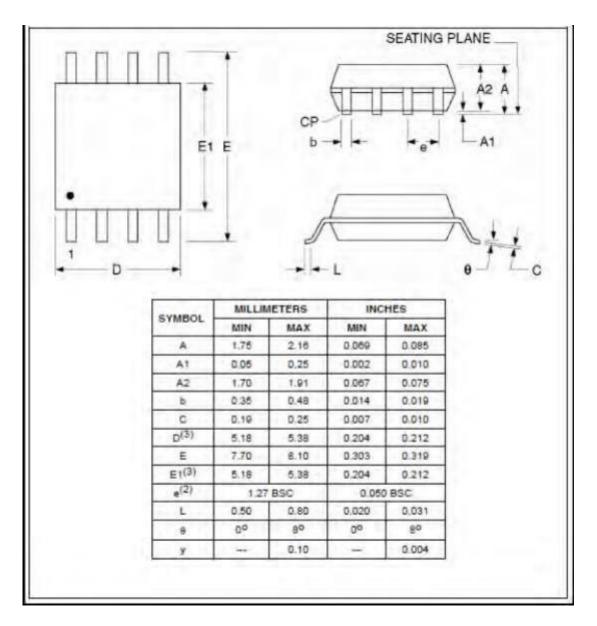

## 19. Package size 8-Pin SOIC 208-mil

联系我们: 联系人:JESSE EMAIL:service\_jesseli@gxschip.com WECHAT:f40044269 FACEBOOK:GXSC VK:@id836505054